Biography

Ipoom Jeong is an Assistant Professor in the Department of System Semiconductor Engineering at Yonsei University and a member of the Institute of Electrical and Electronics Engineers (IEEE). He received his Ph.D. in Electrical and Electronic Engineering from Yonsei University in 2020.

His professional experience includes serving as a Hardware Engineer in the Memory Business Division at Samsung Electronics (2020–2021), a Research Professor in the Department of Electrical and Electronic Engineering at Yonsei University (2021–2022), and a Postdoctoral Research Associate at the University of Illinois Urbana-Champaign (2022–2024).

- Energy-Efficient CPU/GPU Microarchitectures

- High-Performance System Architectures

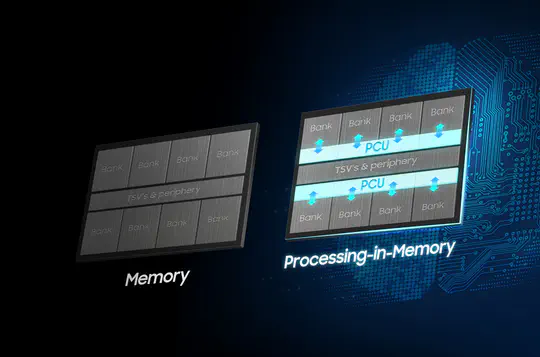

- Near-Data Processing (e.g., PIM, SmartSSD, and SmartNIC)

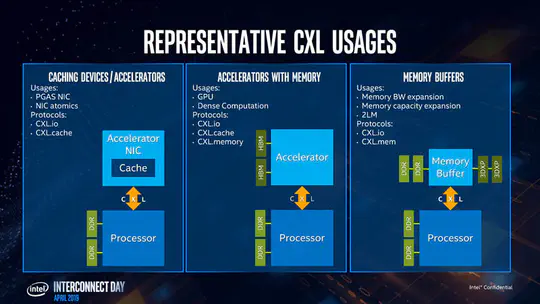

- Interconnect Technologies (e.g., CXL)

PhD in Electrial and Electronic Engineering, 2020

Yonsei University

BS in Electrial and Electronic Engineering, 2014

Yonsei University

Experience

- Department of System Semiconductor Engineering

- School of Electrical and Electronic Engineering

- Research Topics: Energy-Efficient CPU/GPU Microarchitectures, High-Performance System Architectures, Near-Data Processing, Interconnect Technologies

- Coordinated Science Lab (CSL)

- Principal Investigator (PI): Professor Nam Sung Kim

- Research Topics: Architectural Optimizations for Datacenters, CXL-Based Device Architectures, Smart-I/O Devices (SmartSSD, SmartNIC, etc.)

- BK21 Y-BASE R&E Institute, Department of Electrical and Electronic Engineering

- Research Topics: Energy-Efficient CPU/GPU Microarchitectures, Processing-in-Memory (PIM) Architectures

- Advanced Solution Development Team, Memory Business

- Research Topics: CXL-Based Accelerator/Memory Expansion Device Architectures, Computational Storage Drive (SmartSSD 2.0) SoC Architecture

- Embedded Systems and Computer Architecture Lab (eSCaL)

- Advisor: Professor Won Woo Ro

- Research Topics: Energy-Efficient CPU/GPU Microarchitectures, Multi-Core Architectures

- Undergraduate courses: Computer Architecture (EEE3530, 14-1st, 16-1st), Electrical and Electronic Engineering Experiments: Fundamentals (EEE2111, 14-2nd, 15-2nd), Graduation Research (15-1st)

- Graduate courses: Advanced Computer Architecture (E6501, 17-1st), System Design and Applications Lab (EEE6611, 18-1st, 18-2nd)

- Embedded Systems and Computer Architecture Lab (eSCaL)

- Advisor: Professor Won Woo Ro

- Research Topics: Exploiting Back-end Fusion in Multi-Core Processors

Recent Publications

Featured Publications

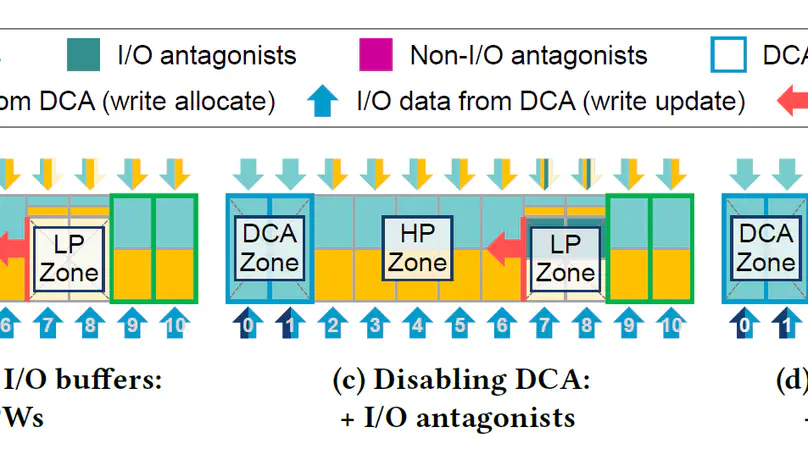

This work uncovers two previously unknown sources of Last-Level Cache (LLC) contention in Intel Xeon CPUs caused by high-bandwidth I/O devices and proposes A4, a runtime LLC management framework that mitigates these issues. A4 improves performance for latency-sensitive workloads by 51% without significantly affecting low-priority workloads.

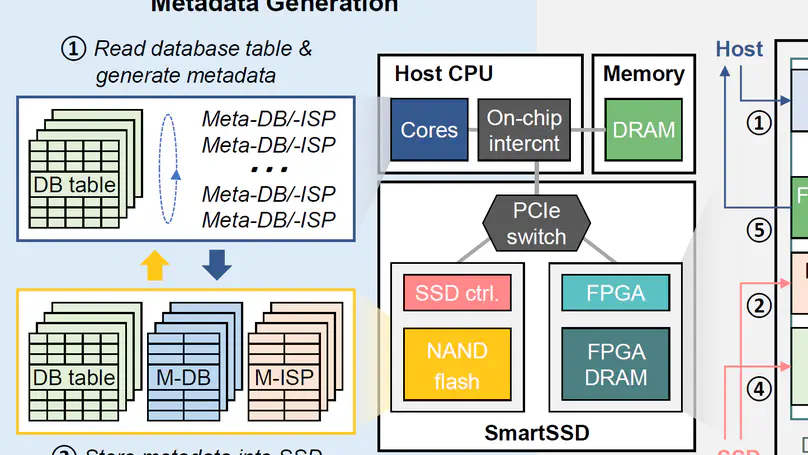

This work introduces Universal Predicate Pushdown (UPP), a flexible in-storage processing (ISP) approach that accelerates modern analytical queries by offloading complex filter predicates to FPGA-based storage using a custom instruction set. By efficiently handling diverse operators and data formats, UPP achieves 1.2×–7.9× speedups on Spark queries over a 100 GB TPC-H dataset without requiring changes to input data formats.

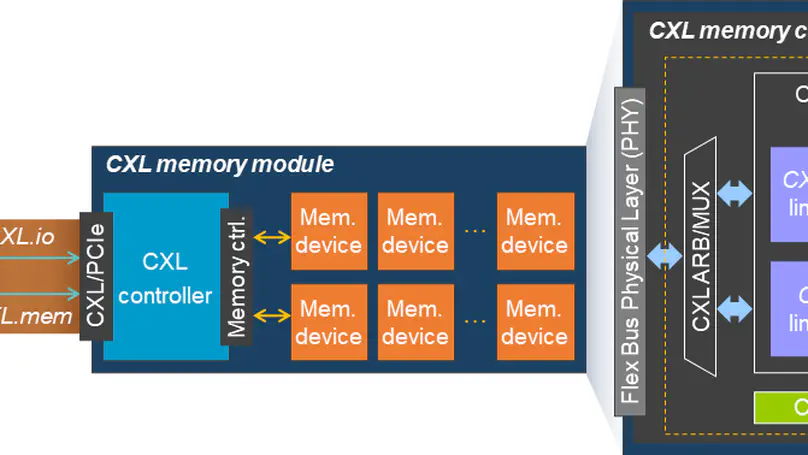

In this work, we evaluate true CXL-ready systems based on the latest 4th-generation Intel Xeon CPU with three CXL memory devices from different manufacturers, which divulges important differences between emulated and true CXL memory devices. Based on these observations, we propose a CXL-memory-aware dynamic page allocation policy, Caption, to use CXL memory more efficiently.

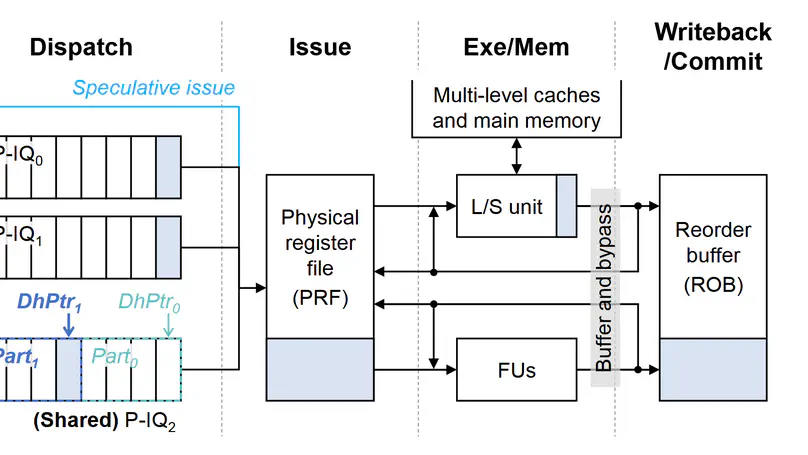

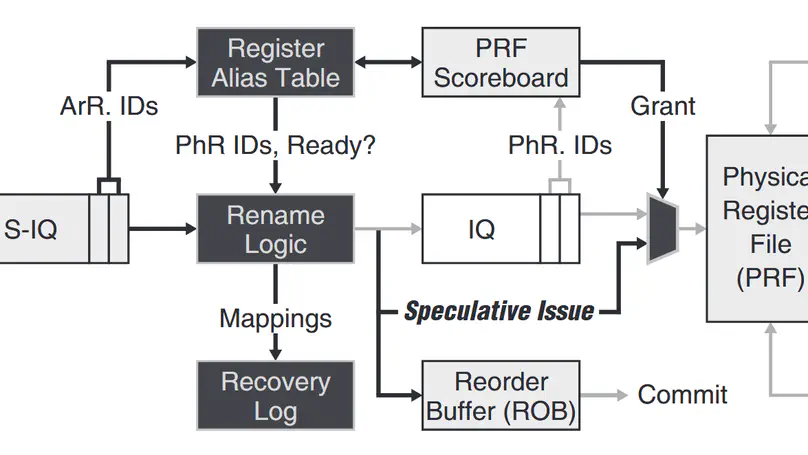

In this work, we propose an energy-efficient microarchitecture named Ballerino, carrying out BALanced and cache-miss toLERable dynamic scheduling via cascaded and clustered IN-Order IQs. The proposed microarchitecture is built upon three key principles that drive dynamic scheduling: instruction readiness, memory/register dependences, and oldest-first selection.

Projects

(Ongoing: 2025.07 - 2030.12)

- Institute for Information & communication Technology Planning & evaluation (IITP)

- Cultivating global, innovative researchers in AI semiconductor technologies

(Ongoing: 2025.06 - 2028.05)

- National Research Foundation of Korea (NRF)

- Developing a simulation framework for CPU-GPU heterogeneous computing that supports processing of the state-of-the-art deep learning algorithms

(Ongoing: 2024.04 - 2026.12)

- Korea Evaluation Institute of Industrial Technology (KEIT)

- Developing CXL-based PNM architecture and simulation platform

(Ongoing: 2024.04 - 2025.12)

- Institute for Information & communication Technology Planning & evaluation (IITP)

- Developing software architecture for data-flow-based PIM devices

(2020.09 - 2021.08)

- Research and development project at Samsung Electronics

- Designing an SoC (System-on-Chip) for next-generation CSDs (Computational Storage Drives)

- A prototype was announced at Flash Memory Summit (FMS) 2022

(2020.03 - 2020.08)

- Research and development project at Samsung Electronics

- Developing CXL (Compute eXpress Link) Type 2 accelerator and Type 3 memory expansion device by leveraging NAND flash

(2019.02 - 2020.02)

- Research project at Yonsei University joint with SK Hynix

- Developing a simulation framework for CPU-GPU heterogeneous computing that supports processing of the state-of-the-art deep learning algorithms

(2018.07 - 2019.06)

- Research project at Yonsei University joint with SK Hynix

- Exploring an energy-efficient approximate memory architecture for deep learning applications

(2017.09 - 2018.08)

- Research project at Yonsei University joint with Samsung Electronics

- Developing ASIPs (Application-Specific Instruction-Set Processors) for cryptographic algorithms (e.g., AES, SHA-256, and RSA-2048)

(2015.07 - 2015.12)

- Research project at Yonsei University joint with ETRI

- Developing and verifying optimization techniques for improving data plane acceleration in virtualized network environment

(2014.07 - 2017.11)

- Research project at Yonsei University joint with LG Electronics

- Inter- and Intra-core optimization techniques for higher energy efficiency of mobile APs (Application Processors)

Recent & Upcoming Events

Scholarships and Awards

[2021.11] Encouragement Prize at the Outstanding Patent Award (SK Hynix)

- Memory Device Including a Plurality of Area Having Different Refresh Periods, Memory Controller Controlling the Same and Memory System Including the Same

- US patent, Registered in 2022.03.15 (Application no: 16/988478, Registration no: 11276452)

[2020.02] Bronze Prize at the 26th Samsung Humantech Paper Award (Samsung Electronics)

- Ipoom Jeong, Seihoon Park

- CASINO Core Microarchitecture: Generating Out-of-Order Schedules Using Cascaded In-Order Scheduling Windows

[2019.11] Excellent Graduate Researcher Scholarship (Yonsei University)

[2018.02] Encouragement Prize at the 24th Samsung Humantech Paper Award (Samsung Electronics)

- Ipoom Jeong, Changmin Lee

- Cg-CMT: Expanding Instruction Window via Coarse-Grained Instruction Commit

[2010.03 - 2014.02] National Scholarship for Science and Engineering (KOSAF)

Activities

Program Committee

- IEEE/ACM International Symposium on Computer Architecture (ISCA) 2026

External Review Committee

- IEEE/ACM International Symposium on Microarchitecture (MICRO) 2025

- IEEE Transactions on Emerging Topics in Computing (TETC)

- IEEE Transactions on Computers (TC)

- ACM Transactions on Storage (TOS)

- IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS)

- IEEE Computer Architecture Letters (CAL)

- ACM Transactions on Architecture and Code Optimization (TACO)

- Microprocessors and Microsystems

Conference Chair

- Excursion chair: IEEE/ACM International Symposium on Microarchitecture (MICRO) 2025

- Session chair: Korea Computer Congress (KCC) 2025

- Publication chair: Korean Institute of Information Scientists and Engineers (KIISE) CSS Conference 2025

- Session chair: Artificial Intelligence Circuits and Systems (AICAS) 2022

Invited Talk/Lecture

- Computer Architectures for Artificial Intelligence, Seoul National University 2025

- IC Design Education Center (IDEC) Academy 2025

- Institute of Electronics and Information Engineers (IEIE) SoC Conference 2025

- Yonsei University AI Plus Forum 2025

- Korean Institute of Information Scientists and Engineers (KIISE) CSS Conference 2025

- IC Design Education Center (IDEC) Academy 2024

- Yonsei University EE Open Lab 2024

- Institute of Electronics and Information Engineers (IEIE) SoC Conference 2024

Tutorial Organizer

- On-chip Accelerators in 4th Gen Intel® Xeon® Scalable Processors: Features, Performance, Use Cases, and Future!

- 50th International Symposium on Computer Architecture (ISCA 2023)

Contact

- ipoom@yonsei.ac.kr

- 02-2123-5853

- 50, Yonsei-ro, Seodaemun-gu, Seoul, 03722

![[ISCA 2023 Tutorial] On-chip Accelerators in 4th Gen Intel® Xeon® Scalable Processors: Features, Performance, Use Cases, and Future!](/talk/isca-2023-tutorial-on-chip-accelerators-in-4th-gen-intel-xeon-scalable-processors-features-performance-use-cases-and-future/featured_hu858e35732560ce6cb32414f0eaab3acc_333469_150x0_resize_q75_h2_lanczos_3.webp)

![[UIUC HACC Seminar] VersatileSSD: Breaking I/O Barrier by Leveraging SmartSSD](/talk/uiuc-hacc-seminar-versatilessd-breaking-i/o-barrier-by-leveraging-smartssd/featured_huc505ebe400d22100d0349334e53dd218_658998_150x0_resize_q75_h2_lanczos_3.webp)